## An Approach towards Disassembly of Malicious Binary Executables

#### A Thesis

Presented to the

**Graduate Faculty of the**

University of Louisiana at Lafayette

In Partial Fulfillment of the

**Requirements for the Degree**

**Master of Science**

Aditya Kapoor

**Fall 2004**

© Aditya Kapoor

2004

**All Rights Reserved**

# An Approach towards Disassembly of Malicious Binary Executables Aditya Kapoor

| APPROVED:                                                       |                                                            |

|-----------------------------------------------------------------|------------------------------------------------------------|

| Arun Lakhotia, Chair<br>Associate Professor of Computer Science | William R. Edwards Associate Professor of Computer Science |

| Dmitri Perkins Assistant Professor of Computer Science          | C. E. Palmer Dean of the Graduate School                   |

#### Acknowledgements

I thank my advisor, Dr. Arun Lakhotia for his valuable guidance, extraordinary support, inspiration, and encouragement. This thesis would never have been conceptualized without the ideas and motivation that he provided me. I greatly appreciate his patience and the trust he showed in me throughout my thesis. He was always there to support me both morally and academically whenever I was in a fix. My gratitude for him cannot be expressed in a paragraph.

I thank my parents and my sister for their never-ending encouragement, trust, and support during my lows and my highs in the research period. I am grateful to Dr. Andrew Walenstein for reviewing my thesis document in a short time and giving me helpful insights. Thanks to Eric Uday, Prashant Pathak, Nitin Jyoti, and Firas Bouz who gave me helpful feedback during all times in my thesis and shared intriguing discussions about the challenges I faced.

Finally, I would also like to thank my roommates Bunty Agrawal, Alok S. Singh, and Jai Dialani for their constant words of support and encouragement in the last two years and the good food they cooked for me.

## TABLE OF CONTENTS

| 1 | INTRODUCTION                                        | 1  |

|---|-----------------------------------------------------|----|

|   | 1.1 MOTIVATION                                      | 1  |

|   | 1.2 RESEARCH OBJECTIVES                             | 4  |

|   | 1.3 RESEARCH CONTRIBUTIONS                          | 4  |

|   | 1.4 IMPACT OF THE RESEARCH                          | 4  |

|   | 1.5 ORGANIZATION OF THESIS                          | 5  |

| 2 | BACKGROUND                                          | 6  |

|   | 2.1 DISASSEMBLY OVERVIEW                            | 6  |

|   | 2.2 DISASSEMBLY CHALLENGES                          | 7  |

|   | 2.3 METHODOLOGIES OF STATIC DISASSEMBLY             | 9  |

|   | 2.3.1 Flow Insensitive Analysis                     | 9  |

|   | 2.3.2 Flow Sensitive Analysis                       | 10 |

|   | 2.3.3 Combined Linear Sweep and Recursive Traversal |    |

|   | 2.3.4 Interactive Disassembly                       | 12 |

|   | 2.3.5 Disassembly Heuristics                        | 13 |

| 3 | PE ARCHITECTURE AND INTEL INSTRUCTION FORMAT        | 14 |

|   | 3.1 PE FILE FORMAT                                  | 14 |

|   | 3.2 Intel Instruction format                        | 15 |

|   | 3.3 INTEL OPCODE MAPS                               |    |

|   | 3.4 Addressing modes                                | 18 |

| 4 | SEGMENTATION OVERVIEW                               | 19 |

|   | 4.1 SEGMENTATION EFFICACY                           | 19 |

|   | 4.2 SEGMENT STRUCTURE                               | 21 |

|   | 4.3 SEGMENT RELATIONSHIPS                           | 21 |

|   | 4.4 SEGMENT CONSTRUCTION                            | 22 |

|   | 4.5 EXPLANATION OF ALGORITHM WAYPOINTS              |    |

|   | 4.6 SEGMENT OVERLAPS AND SPECIAL CASES              | 29 |

|   | 4.7 ILLUSTRATIVE EXAMPLE                            | 31 |

| 5 | SEGMENT PRUNING VIA SEGMENT CHAINING                | 33 |

|   | 5.1 SEGMENT-CHAINING                                | 33 |

|   | 5.2 ALGORITHM: CHAINING AND PRUNING                 |    |

|   | 5.3 EXAMPLE: SEGMENT CHAINING AND PRUNING           |    |

| 6 | EVALUATION AND RESULTS                              | 38 |

|   | 6.1 Theoretical Limitations and Assumptions         | 38 |

|   | 6.1.1 Attacking the Assumptions                     |    |

|   | 6.1.2 Attacking the Implementation                  |    |

|   | 6.2 EXPERIMENTAL SETUP AND ANALYSIS                 |    |

|   | 6.2.1 Setup                                         | 41 |

|    | 6.2.2  | Analysis Parameters                   | 42 |

|----|--------|---------------------------------------|----|

|    | 6.2.3  | Data Analysis: "Clean" Executable     | 44 |

|    | 6.2.4  | Data Analysis: "Malicious" Executable | 47 |

|    | 6.2.5  | Data Analysis: Non-Executables        | 49 |

|    | 6.2.6  | Inference of Data Analysis            | 52 |

| 7  | RELA   | TED WORK                              | 54 |

| 8  | CONC   | CLUSION AND FUTURE WORK               | 58 |

| BI | BLIOGE | RAPHY                                 | 60 |

| ΑB | STRAC  | Т                                     | 62 |

| BI | OGRAP  | HICAL SKETCH                          | 63 |

## LIST OF FIGURES

| FIG.                          | 1-1. STAGES IN STATIC ANALYSIS OF BINARY [15]                                                                                                                                                                                                                                                                                                   | 2                                            |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Fig.                          | 1-2. OBFUSCATION THROUGH JUNK INSERTION.                                                                                                                                                                                                                                                                                                        | 3                                            |

| Fig.                          | 2-1. AN EXAMPLE SHOWING DISASSEMBLY DRAWBACKS USING LINEAR SWEEP                                                                                                                                                                                                                                                                                | 9                                            |

| Fig.                          | 2-2. OBFUSCATION BY JUNK BYTE INSERTION (BEAGLE.H)                                                                                                                                                                                                                                                                                              | . 10                                         |

| Fig.                          | 2-3. COMPARISON OF TARGET RESULTS OF DIFFERENT DISASSEMBLY TECHNIQUES                                                                                                                                                                                                                                                                           | . 12                                         |

| Fig.                          | 3-1. FILE FORMAT OF A PE FILE.                                                                                                                                                                                                                                                                                                                  | . 15                                         |

| FIG.                          | 3-2. Intel instruction format                                                                                                                                                                                                                                                                                                                   | . 16                                         |

| FIG.                          | 3-3. ARCHITECTURE OF MOD R/M BYTE AND SIB BYTE                                                                                                                                                                                                                                                                                                  | . 17                                         |

| Fig.                          | 3-4. A 32 BIT INSTRUCTION AND ITS STRUCTURE                                                                                                                                                                                                                                                                                                     | . 17                                         |

| Fig.                          | 4-1. Example showing control flow of program starting at byte $0$                                                                                                                                                                                                                                                                               | . 20                                         |

| Fig.                          | 4-2. Example showing control flow of program starting at byte 1                                                                                                                                                                                                                                                                                 | . 20                                         |

| Fig.                          | 4-3. STRUCTURE OF A SEGMENT                                                                                                                                                                                                                                                                                                                     | . 21                                         |

| Fig.                          | 4-4. STEPS OF SEGMENT CREATION                                                                                                                                                                                                                                                                                                                  | . 23                                         |

| Fig.                          | 4-5. SEGMENT TERMINATION                                                                                                                                                                                                                                                                                                                        | . 24                                         |

| Fig.                          | 4-6. PSEUDOCODE FOR SEGMENTATION ALGORITHM, LEFTMOST COLUMN SPECIFIES                                                                                                                                                                                                                                                                           | S                                            |

|                               | CODE WAYPOINTS                                                                                                                                                                                                                                                                                                                                  | . 26                                         |

| FIG.                          | 4-7. MAIN PROGRAM PSEUDOCODE FOR COMPUTING SEGMENTS                                                                                                                                                                                                                                                                                             | . 27                                         |

| FIG.                          | 4-8. ILLUSTRATIVE EXAMPLE OF SEGMENT OVERLAPS                                                                                                                                                                                                                                                                                                   | . 30                                         |

|                               |                                                                                                                                                                                                                                                                                                                                                 |                                              |

| FIG.                          | 4-9. EXAMPLE SHOWING SPECIAL CASE OF OVERLAPPING                                                                                                                                                                                                                                                                                                | . 30                                         |

|                               | 4-9. EXAMPLE SHOWING SPECIAL CASE OF OVERLAPPING                                                                                                                                                                                                                                                                                                |                                              |

| FIG.                          |                                                                                                                                                                                                                                                                                                                                                 |                                              |

| FIG.                          | 4-10. EXAMPLE 2: EXCERPT OF ASSEMBLY CODE FROM A SAMPLE PROGRAM                                                                                                                                                                                                                                                                                 | . 31                                         |

| Fig.<br>Fig.                  | 4-10. EXAMPLE 2: EXCERPT OF ASSEMBLY CODE FROM A SAMPLE PROGRAM                                                                                                                                                                                                                                                                                 | . 31                                         |

| Fig.<br>Fig.<br>Fig.          | 4-10. EXAMPLE 2: EXCERPT OF ASSEMBLY CODE FROM A SAMPLE PROGRAM                                                                                                                                                                                                                                                                                 | . 31                                         |

| Fig.<br>Fig.<br>Fig.          | 4-10. EXAMPLE 2: EXCERPT OF ASSEMBLY CODE FROM A SAMPLE PROGRAM                                                                                                                                                                                                                                                                                 | . 31                                         |

| FIG. FIG. FIG.                | 4-10. EXAMPLE 2: EXCERPT OF ASSEMBLY CODE FROM A SAMPLE PROGRAM                                                                                                                                                                                                                                                                                 | . 31                                         |

| FIG. FIG. FIG.                | 4-10. EXAMPLE 2: EXCERPT OF ASSEMBLY CODE FROM A SAMPLE PROGRAM                                                                                                                                                                                                                                                                                 | . 31<br>. 32<br>. 34<br>. 36                 |

| FIG. FIG. FIG. FIG.           | 4-10. Example 2: excerpt of assembly code from a sample program 4-11. Effect of applying segmentation algorithm on given code block, Grey area shows end of segment.  5-1. Various stages of segmentation.  5-2. Pseudocode for segment-chaining algorithm, Leftmost column  Specifies code waypoints.  5-3. Pseudocode for deleting a segment. | . 31                                         |

| FIG. FIG. FIG. FIG. FIG. FIG. | 4-10. EXAMPLE 2: EXCERPT OF ASSEMBLY CODE FROM A SAMPLE PROGRAM                                                                                                                                                                                                                                                                                 | . 31<br>. 32<br>. 34<br>. 36<br>. 37<br>. 39 |

| FIG. | 6-4 SEGMENT COMPARISONS: CLEAN EXECUTABLES                 | . 46 |

|------|------------------------------------------------------------|------|

| FIG. | 6-5. CODE INFLATION INDEX: CLEAN EXECUTABLES               | . 46 |

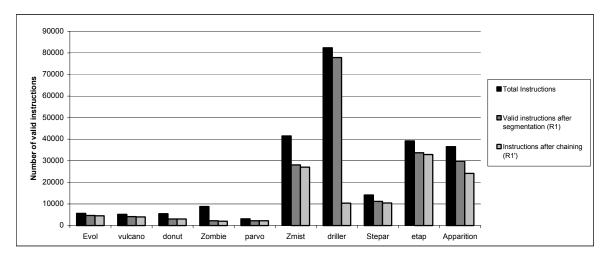

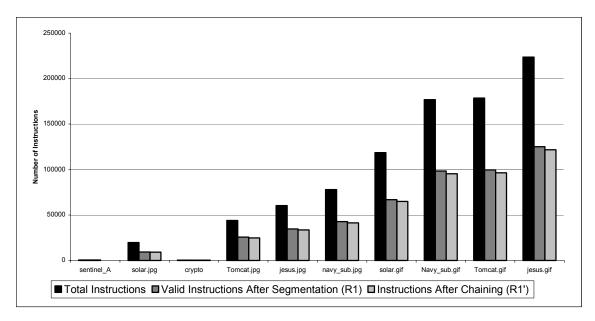

| FIG. | 6-6 Pruning of invalid instructions: malicious executables | . 48 |

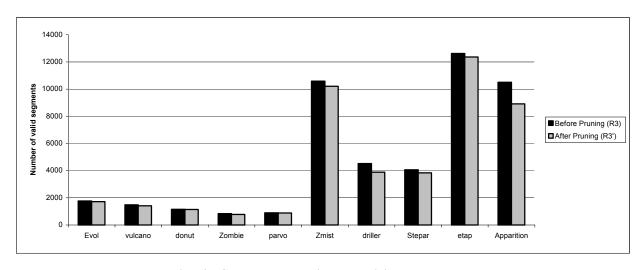

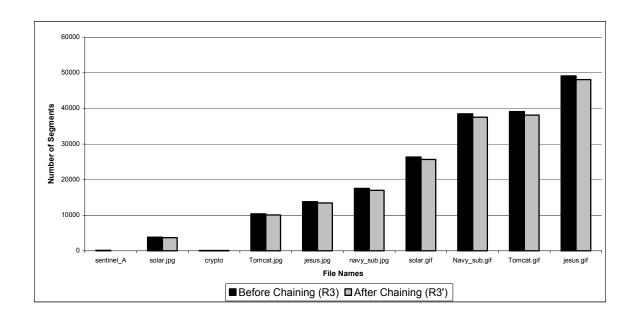

| FIG. | 6-7 SEGMENT COMPARISONS: MALICIOUS EXECUTABLES             | . 48 |

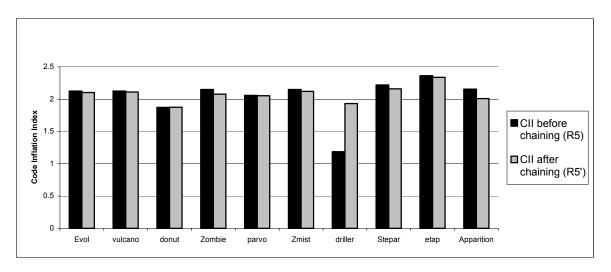

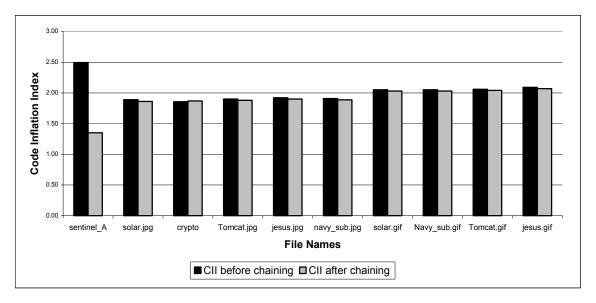

| FIG. | 6-8 CODE INFLATION INDEX: MALICIOUS EXECUTABLES            | . 49 |

| FIG. | 6-9 SEGMENT COMPARISONS: NON-EXECUTABLES                   | . 51 |

| FIG. | 6-10 Pruning of invalid instructions: non-executables      | . 51 |

| Fig. | 6-11 Code inflation index: non-executables                 | . 52 |

## LIST OF TABLES

| Table 6-1. Results: Clean Executable (instruction, segments, and overlaps). 4- |

|--------------------------------------------------------------------------------|

| TABLE 6-2 RESULTS: MALICIOUS EXECUTABLE (INSTRUCTION, SEGMENTS, AND OVERLAPS   |

| 4′                                                                             |

| TABLE 6-3 IMAGE FILES USED FOR DATA ANALYSIS. 49                               |

| TABLE 6-4 RESULTS: NON-EXECUTABLE (INSTRUCTION, SEGMENTS, AND OVERLAPS) 50     |

#### 1 Introduction

#### 1.1 Motivation

In the recent past computer security has become an issue of foremost importance for individuals, businesses, and governments. Hostile programmers, who write programs with malicious intents of collecting private information, spread spam, etc. breach the existing security measures. Whenever these hostile programmers, specifically virus/worm writers, succeed in spreading a virus or a worm, there is a significant loss to businesses. For example, mi2g website [6] quotes that within one quarter the NetSky worm and all its A - Q variants put together, had already caused between \$35.8 billion and \$43.8 billion of estimated economic damages worldwide. The website also quotes that, in March, combined losses due to the three worms Beagle, MyDoom, and NetSky crossed the \$100 billion mark within a week.

The war between hostile programmers and antivirus writers resembles any classic arms escalation. The first step in countering the malicious attacks is to identify the malicious programs. Antivirus companies use several dynamic and static analysis techniques to identify malware [25]. Most of the Anti-Virus (AV) tools depend upon knowledge of what are called "virus signatures," which are nothing but patterns of system calls. If these AV tools can find a particular signature in their database of currently known patterns, they raise an alarm. To identify signatures from a malicious program or to understand and counteract the malicious behavior, we need to analyze the executable. This typically requires converting the byte sequence of an executable to an intermediate representation.

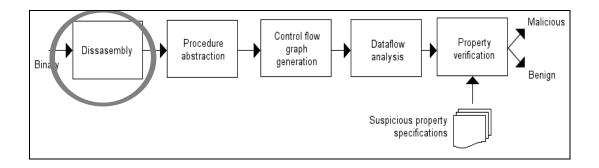

Fig. 1-1. Stages in static analysis of binary [15].

According to [15], the architecture shown in Fig. 1-1 is a proposed staged architecture for binary malware analysis. Disassembly is the first step, and it generally must occur before subsequent analysis can take place. Current disassemblers are used for different purpose, such as binary rewriting for efficiency [20], portability [11, 23] or program maintenance when source code is not available. The problem of disassembly becomes a research issue when the disassemblers are used to analyze malicious codes. The current disassembly algorithms are based on many assumptions such as entry point and control flow information, which are easy targets of malicious code writers.

Techniques used by code-obfuscators [19], for the purpose of protecting intellectual property, can be used by malicious code writers. These writers having malicious intents also rely on many of the existing virus creation tools [5] and obfuscation techniques, such as junk byte insertion, computed jumps, and self-modifying code, to hinder the disassembly process of the current algorithms [14, 17].

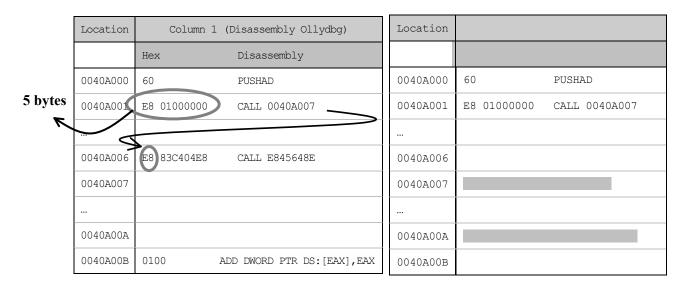

There are several examples of virus code and obfuscators that motivate this research. A Few recent examples are self-modifying code of mass mailing worm Netsky.Z and Beagle.H (Junk byte Insertion) that puts the current disassemblers into disarray. Fig. 1-2 shows the disassembled code of Beagle.H obtained from the open

source debugger Ollydbg. Column 1 shows the incorrect disassembly generated from Ollydbg, while column 2 shows the correct disassembly. It is evident from the figure that the virus writer has successfully hidden instructions starting at location 0040A006 and 0040A00A.

Fig. 1-2. Obfuscation through junk insertion.

The foremost challenge for a disassembly algorithm is to distinguish between code and data, where data can be embedded in code. In the automated analysis of malice the disassembly algorithm should be:

- *Safe*: all the possible instructions should be disassembled such that no code is hidden from the analysis.

- *Precise*: minimum data being incorrectly recognized as code.

The algorithm proposed in this thesis is termed "segmentation algorithm" and it assures safe disassembly. It analyzes each byte for potentially starting an instruction and, thus, finds all the code. Segmentation approach does not leave any code behind from disassembling. For preciseness, it divides the program into segments to remove illegal instructions.

In an environment that is code intensive, there is a high possibility of data being interpreted as code, since out of 512 possible Intel opcodes 398 are valid opcodes. Also, since each byte can start a valid instruction, there is also a need to check on what we call "Code Inflation," (i.e., how many bytes are present in more than one instruction).

#### 1.2 Research Objectives

The aim of this research is to propose and implement a disassembly method that leaves no code behind from being disassembled, making it harder for malicious code or obfuscated binaries to hide their code, thus raising the bar for hostile programmers.

#### 1.3 Research Contributions

The main contribution of this thesis is a novel approach towards disassembly of malicious and obfuscated binary executables. The main advance comes from a segment-based framework that makes the disassembly process independent of flow analysis and entry point location and, hence, difficult to attack by common obfuscation routines.

Instead of the traditional ordered instruction sequence, the output of the disassembler is a collection of potentially overlapping segments, where each segment defines a unique disassembly of some portion of the executable. The technique examines each and every byte of the program, and it treats each byte as a potential instruction. The approach makes a minimum number of assumptions and, hence, is more robust against obfuscation attacks.

#### 1.4 Impact of the Research

The proposed disassembly technique provides a novel disassembly method that can be used to give more precise disassembly in the presence of obfuscations that use indirect jumps, jump in the middle of instruction, self-modifying code, or control flow

obfuscations. The segmentation-based disassembler can be used to augment the current AV analysis systems, or to reverse engineer obfuscated code. The assembly code, generated from the proposed disassembler, can then be fed to subsequent stages of the pipeline shown in Fig. 1-1.

#### 1.5 Organization of Thesis

Chapter 2 provides an overview of disassembly research problems and introduces the main prior disassembly approaches. Intel instruction format and win32 binary executable architecture are explained in chapter 3. The main segmentation algorithm is explained in chapters 4 and 5. Chapter 4 introduces our framework for identifying segments of code and chapter 5 describes heuristics to reduce false positives by pruning segments that lead to data or other corrupt segments. Chapter 6 discusses the evaluation method and results. Chapter 7 presents related work. Future Work and Conclusions are covered in chapter 8, followed by the bibliography.

#### 2 Background

This chapter outlines the process of disassembling binary executables. It also describes the goals and challenges for disassembling malware, along with providing an overview of main prior disassembly techniques.

#### 2.1 Disassembly Overview

Reverse engineering binary executables is a necessary step for rewriting binaries for efficiency [20], or portability [11, 23]. It is also used for maintaining programs where source code is not available, and for detecting malicious programs. Reverse engineering may include recovering the inherent structure and design of program. Techniques for recovering source from binary generally fall into two categories, i.e., either disassembly [14, 17, 22, 24] or decompilation.

Almost all the antivirus groups use disassemblers frequently to analyze the behavior of suspect programs [25]. The algorithms used in the disassemblers, however, are not written with malicious program in mind. This leads to several problems due to code obfuscation such as junk insertion and hiding target of jump instruction [15]. We experienced this first hand, when studying the disassembly of the win32.evol worm, using the leading commercial disassembler IdaPro [2]. The code of win32.evol makes a jump into the middle of a valid instruction, throwing the disassembler and the programmer off the trail of valid instructions. More generally, we may expect that using technologies developed for a "friendly" programmer are unlikely to withstand "attacks" from a "hostile" programmer.

#### 2.2 Disassembly Challenges

Disassembly can be divided into two categories: dynamic disassembly and static disassembly. During dynamic disassembly a program is executed, and during execution, the instructions being executed are traced. A main drawback of this approach is that any given run may trace through only a subset of the possible execution paths, and even after several runs there is no guarantee that all the paths are executed. Take, for example, a worm, which executes the malevolent payload only on certain dates. Static analysis techniques can give more complete results for disassembly because they can analyze the binary as a whole.

A major challenge in correctly disassembling malware is rooted in the von Neumann architecture, where instructions are indistinguishable from data [13]. The problem is perhaps worst for self-modifying code, where code is treated as data, and what was once data becomes executable. A disassembly algorithm could fail, either by incorrectly interpreting some instruction as data (*False Negative*) or by incorrectly interpreting some data as an instruction (*False Positive*). When analyzing malicious code, especially when the analysis is automated, false negatives may lead to an unsafe analysis, i.e., the malicious parts of the code might be overlooked. On the other hand, false positives can also be damaging by overwhelming the engineer or the tool analyzing the binary.

Malware authors intentionally try to defect static disassembly. They use tricks like jumping into the middle of a valid instruction or use many computed jumps which make it difficult to determine the jump targets statically. Further tricks used to confuse disassemblers include:

- *Junk insertion:* Obfuscators or hostile programmers insert some "junk" bytes between valid instructions to thwart the disassembly. These junk bytes are normally never executed as they are jumped over.

- Using Exception Handlers to transfer control: An exception, such as an invalid instruction or referencing a protected memory page, causes a trap or fault, which the operating system catches and transfers control to code called exception handler. This obfuscates jumps, which can cause disassembler to altogether miss the code at the jump target

- Self-modifying code. Self-modifying code changes itself dynamically at runtime.

Static disassemblers would need to be able to compute the outputs in order to be able to disassemble correctly.

- There are many other novel approaches proposed by [17] such as:

- Call conversion: This obfuscation technique changes the return location of call instruction. The program does not return to the instruction just after call rather it is manipulated to return at a predefined offset from the calling location. The bytes between the offset and location just after call can be filled by junk bytes to confuse disassembler.

- Opaque predicates: In this technique the obfuscators can change all the unconditional jumps and call to conditional jumps and call. The branch that is always taken is known. Malicious writers insert junk data on the location of branch that is never taken.

- Jump table spoofing: Artificial insertions of jump tables that are not visited at run time.

### 2.3 Methodologies of Static Disassembly

Static analysis of a binary is done through methods that are termed either flow sensitive or flow insensitive.

#### 2.3.1 Flow Insensitive Analysis

Flow insensitive algorithms for disassembly do not take control flow of the program in account. In particular they do not use control statements (jumps, calls etc) to affect the choice of which bytes to disassemble. One widely used flow insensitive method for disassembly is the Linear Sweep (LS) algorithm [17, 22-24]. LS starts disassembling instructions from the first executable byte and continue disassembling it until either the program end is reached or it encounters an invalid instruction code. In case LS implementation encounters such an invalid code, it generally either terminates or continues from the next byte.

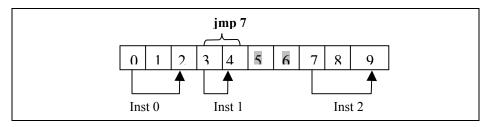

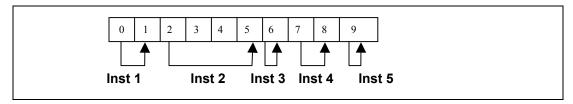

Consider the sequence of 10 bytes illustrated in Fig. 2-1. In the figure each column represents a byte, and each arrow represents an instruction. Bytes 5 and 6 are junk bytes and are not part of the program code. LS starts disassembling from byte 0 and would return Inst 0, Inst 1 and Inst2 as disassembly result along with bytes 5 and 6 (if bytes 5 or 6 starts an instruction). A hostile programmer can craft bytes 5 and 6 to confuse the disassembler, since now we get four instructions Inst 0, Inst1, Inst 2 and instruction consisting of bytes 5 and 6.

Fig. 2-1. An example showing disassembly drawbacks using Linear Sweep

Fig. 2-1 shows code of a variant of mass mailing worm beagle.h. Column 1 shows the output of the open source debugger Ollydbg, while column 2 shows the desired disassembly. At location 0040A001 the length of the instruction is 5 bytes. LS assumes that the next instruction starts at 0040A006 and disassembles from there, resulting in 5 byte call instruction (*CALL E845648E*,) and so the next disassembled instruction starts at 0040A00B which is a junk byte. The junk byte is also a 5-byte call instruction code, which throws off disassembly because the next instruction is supposed to start at 0040A007. Since E8 is an opcode for *call* instruction, it looks like a legitimate instruction starting at 0040A006. The virus writer chose E8 since he has to insert an opcode that starts a valid instruction else LS can raise alarms.

| Location | Column 1    | 1 (Disassembly Ollydbg)    | Column 2 (Actual Disassembly) |               |  |

|----------|-------------|----------------------------|-------------------------------|---------------|--|

|          | Hex         | Disassembly                | Hex                           | Disassembly   |  |

| 0040A000 | 60          | PUSHAD                     | 60                            | PUSHAD        |  |

| 0040A001 | E8 01000000 | CALL 0040A007              | E8 01000000                   | CALL 0040A007 |  |

|          |             |                            |                               |               |  |

| 0040A006 | E8 83C404E8 | CALL E845648E              |                               |               |  |

| 0040A007 |             |                            | 83C4 04                       | ADD ESP,4     |  |

|          |             |                            |                               |               |  |

| 0040A00A |             |                            | E8 01000000                   | CALL 0040A010 |  |

| 0040A00B | 0100        | ADD DWORD PTR DS:[EAX],EAX |                               |               |  |

Fig. 2-2. Obfuscation by junk byte insertion (Beagle.H)

#### 2.3.2 Flow Sensitive Analysis

Flow sensitive analysis uses control flow information to determine which bytes to disassemble. One of the widely used flow sensitive algorithms is Recursive Traversal (RT) [11, 17, 22-24]. It starts disassembly at the program's main entry point and

disassembles linearly, but as soon as it hits a branch instruction, it jumps to target and again starts disassembling from there. RT disassembles a program, by following all the possible targets of branch instructions encountered. Consider again Fig. 2-2, if we follow RT we get the correct disassembly as shown in column 2. Since at location 0040A001 it will jump to location 0040A007 and starts the disassembly from there. Thus RT ensures unreachable program code at location 0040A006 is not included in the disassembled code.

The main weakness of Recursive Traversal is that it requires precise and accurate control flow information, i.e., it must first precisely identify control flow successors for each control transfer operation in the program. But determining correct control flow is made extremely challenging by indirect jumps, indirect jumps via jump table that does not have bounds check associated with them, and self-modifying code. There are cases when a set of possible targets cannot be statically determined, and hence result in both false positives (in case of overestimation of targets) and false negatives (in case of underestimation of targets). Also RT can be defeated by inserting junk bytes just after a call instruction. Since it assumes that control returns to the next instruction after a call.

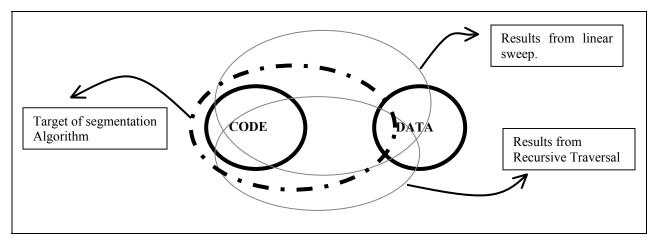

Fig. 2-3 illustrates the under and over-estimation of LS and RT, the results of LS and RT are illustrated by inner gray ovals. Overestimation of targets can lead to target locations that are not part of the code and thus can disassemble some data.

Underestimation on the other hand might miss target locations where valid code is starting. We say disassembly is precise and safe if we don't have any false negatives and minimum false positives. The dotted oval shows the target of the proposed algorithm.

11

Fig. 2-3. Comparison of target results of different disassembly techniques

#### 2.3.3 Combined Linear Sweep and Recursive Traversal

A hybrid approach that combines both LS and RT is proposed by [22]. The hybrid algorithm disassembles using Linear Sweep and verifies the disassembly a function at a time, using Recursive Traversal. This approach, in some cases, can detect and identify some of incorrect disassembly. This approach also fails in case of call conversion, opaque predicates and self-modifying code.

#### 2.3.4 Interactive Disassembly

Due to drawbacks of current algorithms, some reverse-engineering tools use interactive disassembly techniques [2, 9]. One of the most powerful interactive disassemblers is IDA-Pro [2]. The main advantage with interactive disassembly tools is that the users can choose some bytes that they think might be code and start disassembly from that point onwards. Interactive disassembly is primarily a manual process, but the users are allowed to check validity of their thoughts. Interactive disassembly is laborious and may be error prone due to human intervention.

#### 2.3.5 Disassembly Heuristics

LS and RT- based techniques also have false negatives as well as false positives. To reduce these false negatives heuristics can be used to restart the disassembly in the "gaps" of untouched bytes. One such heuristic is termed "Speculative Disassembly" [11]. In this technique, the undissassembled portions of the code are made targets of indirect jumps and a "speculative bit" attached to the target is set. The disassembly of a particular code area is stopped if an invalid instruction is encountered. The disassembly resumes from the next byte. This heuristic, when augmented to LS and RT-based techniques, may lower down the false negatives by finding all possible instructions in the "gap" area.

#### 3 PE Architecture and Intel Instruction Format

The path from a binary to disassembly consists of several steps that convert sequence of bytes to assembly instructions such that it can be easily analyzed. Given a sequence of bytes the conversion of bytes to intermediate representation depends upon the choice of processor architecture. All architectures have certain opcode map for mapping bytes sequence to instructions and vice versa. For our purposes we use Intel architecture [3]. In order to reverse engineer a binary executable we need to understand the steps involved in it. Since most of the virus attacks target PE (win32 portable executable) files, we analyze and disassemble only PE files (although the methods proposed should be readily extendible to DOS executables, ELF).

This chapter introduces:

- PE File format,

- Intel instruction format [3, 18], and the

- Intel Opcode Map [3]

#### 3.1 PE file format

Fig. 3-1 shows the general layout of a PE file. All PE files starts with DOS MZ header followed by a small program called DOS stub. The stub is the small program that gives out an error message if the program cannot be run in DOS mode. Here we only discuss the fields that are required to get the information of the byte sequence to be disassembled. One of the important parts of PE file is the header that contains the time and date stamp of PE file, the size of code, the address of entry point etc. Other important parts to focus in PE files are the section headers contained in the section table. PE executables are divided into chunks of bytes called "sections." Each section has a

different attribute such as whether it is code or data or whether it is read or write enabled. The number of entries in the section table is dependent upon the total number of sections i.e. if there are n number of sections there will be n entries in the section table.

| DOS "MZ" header | Contains the magic number "MZ" (0x 4d 0x 5a) in first two bytes. Last byte contains offset of PE header                                                          |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DOS STUB        | Contains small program saying "this program cannot be run in dos mode".                                                                                          |  |  |  |

| "PE" header     | Contains a magic number PE00 as starting 4 bytes. Info such as number of sections, entry point, image base, time and date stamp etc                              |  |  |  |

| Section Table   | Contains Headers for each section. Each Header contains information for sections like size, RVA, name and characteristics stating it to be code or data section. |  |  |  |

| Section 1       |                                                                                                                                                                  |  |  |  |

| Section 2       | Sections of PE file containing byte code. More than one                                                                                                          |  |  |  |

| •••             | section can have same characteristics.                                                                                                                           |  |  |  |

| Section n       | <u> </u>                                                                                                                                                         |  |  |  |

Fig. 3-1. File format of a PE file.

It is not necessary that a section be labeled as "data" or "code" since section can contain both data as well as code. For disassembling, we need the sections and the information about sections, such as virtual address of the section, size of the section, and its real address in the file. All information about sections can be found in section header.

#### 3.2 Intel Instruction format

Some knowledge of the instruction format of Intel is required to convert byte sequences into meaningful assembly instructions. Intel instruction can vary in length from one byte to fourteen bytes. The structure of every instruction is fixed, and illustrated in the Fig. 3-2 [18].

| Instruction | Prefix    | Opcode       | Mod R/M     | SIB         | Displacement | Immediate |

|-------------|-----------|--------------|-------------|-------------|--------------|-----------|

| No of bytes | 0-4 bytes | 1 or 2 bytes | 0 or 1 byte | 0 or 1 byte | 0-4 bytes    | 0-4 bytes |

Fig. 3-2. Intel instruction format

An instruction can start with an optional prefix of up to four bytes. Instruction prefixes modify default instruction behavior, i.e., they can force default segment of an instruction or can override default size of machine word, to either 16 or 32-bit word. Prefix also determines whether the following opcode is of one byte or two bytes. Specifically, if prefix is "0x0F" the opcode is a two-byte opcode. An opcode decides the primary format of an instruction. It determines whether there is further byte following the opcode or the instruction is a one-byte instruction. An opcode also determine about direction of operation.

If required, optional bytes, such as Mod R/M, SIB, displacement, and immediate can follow the opcode byte. Mod R/M byte decides the addressing mode (direct/indirect etc) of the operand. It specifies about the register to be used in the instruction and indexing modes. Optional byte SIB (Scale Index Base) might follow Mod R/M byte to extend the different addressing modes represented by Mod R/M. Fig. 3-3 shows the architecture of both Mod R/M byte and SIB byte [4, 18]. Following formula is used to compute the SIB value: "(index \*2^scale) + base" and used for representing complex addressing modes.

|   | Mod   | Reg/Opcode |       | R/M  |   |

|---|-------|------------|-------|------|---|

| 7 | 6     | 15         | 3   2 |      | 0 |

|   | Scale | Index      |       | Base |   |

Fig. 3-3. Architecture of Mod R/M byte and SIB byte

Example showing interpretation of an instruction:

Mod byte is a two-bit value (most significant bits in Fig. 3-3). It can have 4 possible values 00, 01, 10 or 11. Which of the optional byte follows Mod R/M is decided by the Mod R/M value. For example, the combination 01 or 10 in the Mod field leads to displacement byte following the Mod R/M byte. Lets consider an example.

| Prefix                                                        | Opcode   | Mod R/M  | SIB      | Displacement                        |

|---------------------------------------------------------------|----------|----------|----------|-------------------------------------|

|                                                               | 10001011 | 00000100 | 10000101 | 01001100 01111011 01000010 00000000 |

| Instruction: mov eax , dword[ 4*eax+427b4c ] = 8b04854c7b4200 |          |          |          |                                     |

Fig. 3-4. A 32 bit instruction and its structure

Fig. 3-4 illustrates disassembly of a sequence of bytes to an assembly instruction. The opcode value specifies that the instruction is a *mov* instruction. The X86 processor and memory manager uses mapping tables to map opcodes, Mod R/M bytes and SIB bytes to corresponding tables and interpret any instruction. This is an interesting example because the Mod field is neither 01 nor 10, yet there is a displacement byte following it. This example highlights the need for opcode maps, containing detailed rules, to map byte-sequences to instructions.

#### 3.3 Intel Opcode Maps

X86 processors divide the instructions into three encoding groups, namely: 1-byte opcode encodings, 2-byte opcode encodings, and escape (floating-point) encodings [3]. Section 3.2 discussed how prefix value affects length of opcode. If the opcode is not preceded by prefix "0x0f" then it is a single byte opcode, and if the opcode is preceded by "0x0f" prefix then it is a two-byte opcode. Each opcode has a lookup map associated with it. For example, if the opcode is 0x08, then the associated table entry will be one of ADD, OR, ADC, SBB, AND, SUB, XOR or CMP. If it is "0x0f 0x80" then the two-byte opcode map is referenced instead and the instruction is *jo* (jump on overflow) in this case.

The opcode map contains all the information about the byte following the opcode if it is part of instruction. Specifically, for each value of opcode the map contains information about register type, whether Mod R/M byte follows or not etc.

#### 3.4 Addressing modes

X86 normally supports two addressing modes for its operands: direct and indirect. It also provides unconditional and conditional branch or jump instructions. Examples of conditional jump instructions are *jz*, *je*, *loopne* etc and examples of unconditional jump instructions are *jmp*, *call*, *ret* etc. Both conditional and unconditional branches can jump either directly or indirectly. Example of direct jmp is *call* 401000 where we know the exact address that it jumps to, in case of indirect jump it can jump via registers as in *call* eax.

#### 4 Segmentation Overview

A key contribution of this thesis is an algorithm for extracting maximal set of valid instructions embedded in basic blocks (termed as segments). The key idea behind segmentation is to find all the possible code in the executable by considering each byte as potentially starting an instruction. The basic steps of segmentation algorithm are:

- Exhaustively check each byte for starting an instruction

- Create segments sequences of instructions

- Chain segments link segments based on jump targets

- Prune segments remove segments leading to invalid instructions

The segmentation approach does not rely on certain common assumptions like entry point information and control flow information.

This chapter elaborates on the following points:

- Segmentation efficacy

- Segment structure

- Segment relationships

- Segment construction

- Overlap special cases

#### 4.1 Segmentation Efficacy

In most prior disassembly approaches, it was effectively assumed that no byte may belong to more than one instruction, and that a binary is effectively a contiguous collection of non-overlapping instruction sequences. A key question to ask, however, is:

Can one byte be in two instructions?

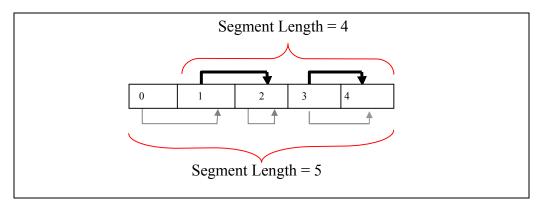

Consider the byte sequence and control flows depicted in Fig. 4-1 and Fig. 4-2. In the figures arrows indicate the start and ending bytes of instructions.

Fig. 4-1. Example showing control flow of program starting at byte 0

Fig. 4-2. Example showing control flow of program starting at byte 1

Assume Fig. 4-1 represents what is considered to be a "correct" instruction set of the program. If the disassembly is off by one byte due to incorrect disassembly of data [17], we might get a different instruction set as shown in Fig. 4-2. Since, 398 out of possible 512 opcodes in the Intel instruction set are valid, therefore *Inst 1'*, *Inst 2'*, and *Inst 3'* could potentially start valid instructions. Fig. 4-2 shows an instruction set starting from byte 1. It can be seen that the disassembly "self-repairs" [17] itself at byte 6. The existing disassembly algorithms would consider Fig. 4-2 to be the correct disassembly, thereby missing the control flow of Fig. 4-1.

To overcome this limitation, it is necessary to consider each byte as potentially starting an instruction. In our approach each byte could potentially start an instruction, thereby presenting an exhaustive way of finding all possible instructions. Hence, it is possible to find all disassembly paths in the binary. The pool of instructions generated by

analyzing all the bytes gives the largest possible instruction set within the binary, i.e., the algorithm cannot have any false negatives.

#### **4.2** Segment Structure

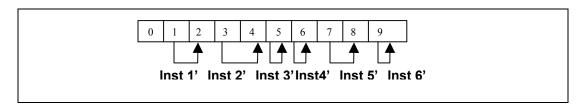

Fig. 4-3 depicts the structure of a segment. Each segment is the maximal sequence of instructions and is terminated by an instruction that represents transfer of control such as *jmp*, *call*, *loopne* etc.

Fig. 4-3. Structure of a segment

All instructions implicitly increment the program counter by one address. We say that an instruction <u>explicitly</u> modifies program counter (PC) if it is a control transfer operation, i.e., PC does not point to the byte immediately after the instruction. For example *jmp*, *call and ret* explicitly modify PC.

#### 4.3 Segment Relationships

Since each byte may theoretically start an instruction, it may also start a segment. The byte starting a segment is denoted as *segStart;* the byte ending a segment is denoted as *segEnd*. A unique segment id *segId* is assigned to each segment.

The *segStart* and *segEnd* are actual locations of bytes in a binary file. For any two segments  $S_i$  and  $S_j$ ,  $S_i=S_j$  iff i=j, for all  $i, j \ge 0$ . If  $j \ge i$ , then the starting byte of  $S_i$  is less than starting byte of  $S_j$ , i.e., in the binary file, segment  $S_i$  starts prior to segment  $S_j$ . We

call each segment a "potential segment", until it is *chained successfully* (section 5) to other potential segments, to regenerate the assembly code. These potential segments can be categorized according to their properties as shown below.

- Overlapping segment: For any Si, Sj, such that j > i, Sj.segStart < Si.segEnd implies Si and Sj are overlapping segments.</li>

- $\forall i,j$ , such that j>i and  $Sj.segStart< S_i.segEnd <math>\Leftrightarrow$  overlapping  $(S_i,S_j)$

- 2. *Intermediate segment:* Sj is an intermediate segment of Si iff j > i, and Si and Sj are overlapping segments. Exactly one instruction is common in both segments. and Sj.segEnd < Si.segEnd.

- $\forall i, j, j > i \text{ and overlapping } (S_i, S_j) \text{ and } |S_i \cap S_j| = 1 \text{ and } S_j.segEnd < S_i.segEnd \Leftrightarrow$  Intermediate(S\_j, S\_i).

- 3. *Master Segment:* Segment  $S_i$  is called a master segment if there exists a segment  $S_i$ , such that  $S_i$  is an intermediate segment of  $S_i$ .

- $\exists$  Sj.Intermediate(Sj,Si) => masterSegment(Si)

#### **4.4** Segment Construction

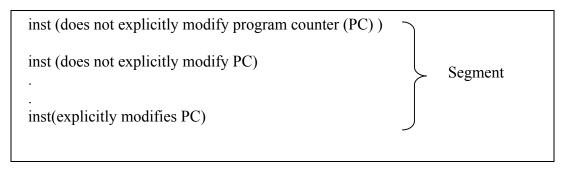

Fig. 4-4 depicts the steps for segment creation starting from the byte B0. In the figure the bytes shown in gray color are not analyzed for possible instruction start. S0 and S1 are intermediate stages of segment creation, while S2 is the final segment.

Fig. 4-4. Steps of segment creation

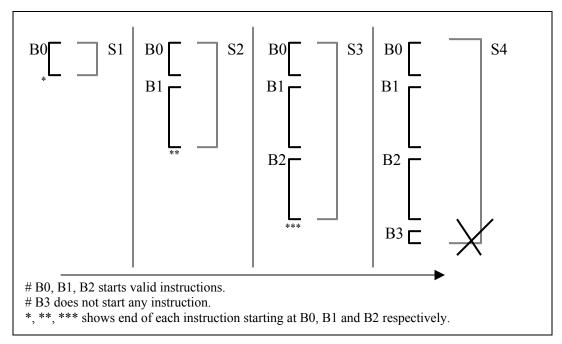

Each byte that starts an instruction may lead to a segment that is either valid or invalid. Fig. 4-5 shows the life cycle of segment creation from *S1* to *S4*. *B0*, *B1* and *B2* start valid instructions (shown by black brackets). The segment is represented by gray bracket, in its various stages of development. Depending upon byte *B3*, the segment is termed either a valid potential segment or an invalid/corrupt segment. If *B3* is the byte that starts a valid instruction then *S4* is a valid potential segment. In case *B3* does not start any instruction *S4* is an invalid/corrupt segment.

Fig. 4-5. Segment termination

The algorithm is shown in Fig. 4-6, and uses the following keywords and methods:

potentialSegmentSize(b): The algorithm assigns a value corresponding to each byte b called potentialSegmentSize(b) or PSS(b) (read as potential segment size of byte b). PSS of each byte is overloaded and has different meaning depending upon its value. There are three cases for this

- Case 1. potentialSegmentSize(b)=0 implies this byte does not start a valid segment, i.e., a segment that has only valid instructions.

- Case 2. potentialSegmentSize(b)=n, where n>0 implies, bytes b to b + n-1 form a potential segment.

- Case 3. potentialSegmentSize(b)=n, where n<0 implies the bytes from b+n (which is less than b, since n<0) to b+n+potentialSegmentSize(b+n)-1 is

a potential segment, if the potential Segment Size(b+n) is not equal to zero.

getPotentialSegmentSize (byte  $\rightarrow Int$ ) gives the number of bytes following upto which, there are, sequence of valid instructions that do not explicitly modify the program counter (PC).

setPotentialSegmentSize (byte, int  $\rightarrow void$ ) sets PSS value corresponding to each byte. We would typically need the longest "potential segment".

masterSegmentStart (segment,  $int \rightarrow void$ ) represents the start of a master segment of an intermediate segment.

```

computePotentialSegment (b, size)

if (!isVisited(b)) {

setVisited(b, true);

if (getPotentialSegmentSize(b) < 0)

1.

if(getPotentialSegmentSize(b+getPotentialSegmentSize(b))==0)

2.

/* corrupt segment. Delete ongoing segment and exit */

setPotentialSegmentSize ((b-size), 0);

} else { /* instruction part of segment terminate ongoing segment and return */

3.

setPotentialSegmentSize((b-size), size);

masterSegmentStart(this,b+getPotentialSegmentSize(b));

}

} else if (!isStartsInstruction(b) ) {

/* corrupt segment. Delete ongoing segment and exit */

4.

setPotentialSegmentSize((b-size), 0);

} else if (modifiesPC(b)) {

/* end of segment found */

5.

setPotentialSegmentSize(b, -size);

/* mark beginning of segment at b-size */

setPotentialSegmentSize((b-size),(size + instructionSize(b)));

} else {

setPotentialSegmentSize(b, -size);

6.

local size=instructionSize(b);

computePotentialSegment(b+local size, size+local size);

}

```

Fig. 4-6. Pseudocode for segmentation algorithm, Leftmost column specifies code waypoints

```

Class segment

main()

int segStart=-1;

Segment segArr[];

int segEnd=-1;

int segId=-1;

for (i = 0; i < length(program); i++) {

int masterSegment=-1;

setVisited(i, false);

setPotentialSegmentSize((i), 0);

segArr=new Segment(length(program) );

for (i = 0; i < length(program); i++) {

if (!isVisited(i)) {

segArr[i].computePotentialSegment(i,0);

/* if segment exists */

segArr[i].segStart= i;

segArr[i].segId=i;

}

```

Fig. 4-7. Main program pseudocode for computing segments

### 4.5 Explanation of algorithm waypoints

The segmentation algorithm is a recursive process. The objective of the segmentation algorithm is to divide the disassembly into chunks of valid segments, where each segment represents a sequence of valid instructions. The algorithm starts the disassembly from a particular starting byte of the program (in the case of PE file it is the first byte of code section) and tries to form segments. In the process of creating a segment, each byte encountered will be flagged as visited. The algorithm analyzes each byte for the following properties.

- Checks whether the byte start an instruction or not.

- If the byte "b" starts an instruction "I", then the algorithm checks for one of the three properties for the instruction "I" to hold.

- 1. If the instruction "I" modifies the PC explicitly, the byte is marked as an end of segment.

- 2. If "I" does not modify the PC, it is examined to determine if it is part of any existing segment. If "I" belongs to any existing segment, the byte "b" is marked as last byte of the segment. The current segment is marked *intermediate segment* and the existing segment is marked as the *master segment*.

- 3. If the instruction is neither part of any existing segment nor it is a PC-modifying instruction, it is added to the current segment under formation. For example, instructions starting from B0, B1, and B2 in Fig. 4-5 are all added to segment S4, which is under formation.

The program visits each byte only once; this makes the analysis of program linear, depending upon file size. The program disassembles linearly until it hits a data byte, or an instruction that modifies PC or any instruction that is part of other existing segments. The left-most column of Fig. 4-6 depicts the algorithm waypoints.

• Waypoints 1, 2, 3. A negative potential segment size value of a byte represents that it had been visited. If it is visited, there are two cases: either the byte is part of any existing segment or it is a data byte. A byte is a data byte if it does not start an instruction or is a part of a corrupt segment. If the current byte being examined is part of an already existing segment, then the byte as well as the segment under formation, is designated a master segment. The current byte is then marked as the end byte of the segment.

- Waypoint 4. If the byte being analyzed in the current segment does not start an instruction, the potential segment size associated with the byte starting the segment (say B0) is assigned zero. This denotes that B0 does not start any segment.

- Waypoint 5. If we encounter a byte B1 that starts an instruction that explicitly modifies PC, we assign the byte B0 the length of segment equal to the address offset between B0 and B1. Positive value at B0 denotes that B0 start a segment of specified positive length.

- Waypoint 6. The program is called recursively until the end of segment is found or it hits a data byte. The negative PSS value assigned to a byte denotes that byte does not start a segment rather is a part of some segment.

Here, each byte is analyzed only once therefore the complexity of the algorithm is O(N), where N is the number of bytes in the program.

## 4.6 Segment Overlaps and Special Cases

While analyzing every byte of the program for starting a segment, the analysis may generate many overlapping segments that may or may not be part of the code. To understand an overlapping segment, let's consider the example in Fig. 4-8. In the figure, B.segStart < A.segEnd, where A and B are overlapping segments (see section 4.2). A starts at byte 0 while B starts at byte 1 (shown with curly braces). The actual control flow of the program is shown with black arrows, while the gray arrows represent secondary control flow, starting from byte 0. Byte 0 is a data byte that generates an instruction along with byte 1.

Fig. 4-8. Illustrative example of segment overlaps

There are several cases that may occur when segments overlap:

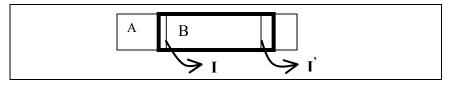

- 1. Fig. 4-9 illustrates the case where *B* is merging into *A* at point *I'*, where *I* is not an instruction of *A*. If the first instruction *I* in Segment *B* is also an instruction of Segment *A*, then segments *A* and *B* must end in same byte. In this case the algorithm would consider *A* as primary segment and discard *B*.

- 2. If I is not an instruction of A then B and A are Overlapping Segments. The first instruction where B "self-repairs" [7] and merges into A, is the end of segment B (I' in Fig. 4-9). B in this case is an intermediate segment while A is a master segment.

- 3. In case *B* merges into an invalid segment *A*, *B* is also marked as invalid.

Fig. 4-9. Example showing special case of overlapping

## 4.7 Illustrative Example

Fig. 4-10 shows an example byte sequence and the target assembly. Fig. 4-11 shows the disassembly generated by our algorithm.

| Memory Byte | Hex Equivalent of Instruction | Assembly Code  |

|-------------|-------------------------------|----------------|

| 401000      | b8 04 00 00 00                | mov eax,4      |

| 401005      | 83 c0 06                      | add eax,6      |

| 401008      | a3 33 20 40 00                | mov x,eax      |

| 40100d      | 01 05 37 20 40 00             | add y,eax      |

| 401013      | c7 05 3b 20 40 00 00 00 00    | mov counter,0  |

| 40101d      | b8 30 10 40 00                | lea eax,label1 |

| 401022      | ff e0                         | jmp eax        |

Fig. 4-10. Example 2: excerpt of assembly code from a sample program

The above code is an initialization code that finally jumps to *label1* to start the processing. This code excerpt is a simple indirect jump. To disassemble the code, label1 might be calculated using data flow analysis.

Fig. 4-11 shows the segments that are created after using the segmentation algorithm. All the segments are numbered in ascending order according to their starting address. Segments 1 and 8 are normal segments that end with instructions that modify the PC explicitly. Grey blocks denote end of a segment.

Whenever any two segments have the same ending instruction, they form an intermediate-master segment pair. For example, segment 2 is an intermediate segment of segment 1, it meets segment 1 at location 401005. Segment 2 is thus an intermediate segment of segment 1. Similarly segments 3, 4, 5, 6, 7, and 9 are intermediate segments to segment 1. Although, segment 8 overlaps with segments 1, 7, and 9 it is not an intermediate segment of any of them. If the disassembly had been off by 2 bytes (due to any disassembly error), the disassembly would start at 401002 and continue until

instruction 40100d (self-repairing point). In such a case, the true instructions are missed if any of the linear sweep or recursive traversal methods is used; the segment algorithm gives all the possible sequences of code. It thus leaves no code behind from disassembling. Also, note that each byte can belong to up to 4 segments in this case.

| Address  | Hex | Segment 1             | Segment 2 | Segment 3              | Segment 4 |  |  |

|----------|-----|-----------------------|-----------|------------------------|-----------|--|--|

| (Bytes)  | nex | Segment 1             | Segment 2 | Segment 3              | segment 4 |  |  |

| 401000:  | ъ8  | mov eax, 4            | 2         | 3                      |           |  |  |

| 401001:  | 04  |                       | [         | [                      | 1         |  |  |

|          | 00  |                       |           |                        |           |  |  |

|          | 00  |                       |           |                        |           |  |  |

|          | 00  |                       |           |                        |           |  |  |

|          | 83  |                       |           |                        | 5         |  |  |

|          | c0  |                       |           |                        |           |  |  |

|          | 06  |                       |           |                        | push es   |  |  |

|          | a3  | :                     |           |                        |           |  |  |

|          | 33  |                       | 1         |                        |           |  |  |

|          | 20  |                       |           |                        |           |  |  |

|          | 40  |                       |           |                        |           |  |  |

|          | 00  |                       |           |                        |           |  |  |

|          | 01  | add dword[402037],eax |           |                        |           |  |  |

|          | 05  |                       |           |                        |           |  |  |

|          | 37  |                       |           |                        |           |  |  |

|          | 20  |                       | 4         | 6                      |           |  |  |

|          | 00  |                       |           |                        |           |  |  |

|          | c7  | mov dword[40203b],0   |           |                        |           |  |  |

|          | 05  | mov dword[402035],0   |           |                        |           |  |  |

|          | 3b  |                       |           |                        |           |  |  |

|          | 20  |                       |           |                        |           |  |  |

|          | 40  |                       |           |                        |           |  |  |

|          | 00  | ·                     | ·         |                        |           |  |  |

| [        | 00  |                       | 7         |                        |           |  |  |

|          | 00  |                       | /         |                        |           |  |  |

|          | 00  |                       |           | 8                      |           |  |  |

|          | 00  |                       |           |                        | 9 🗍       |  |  |

|          | b8  |                       |           |                        |           |  |  |

|          | 30  |                       |           |                        |           |  |  |

|          | 10  |                       |           |                        |           |  |  |

| <b> </b> | 40  |                       |           | inc eax                |           |  |  |

| 401021:  | 00  |                       |           | add bh , bh            |           |  |  |

| 401022:  | ff  | jmp eax               | jmp eax   |                        | jmp eax   |  |  |

| 401023:  | e0  |                       |           | loopne near ptr 401080 |           |  |  |

Fig. 4-11. Effect of applying segmentation algorithm on given code block, Grey area shows end of segment.

### 5 Segment Pruning via Segment Chaining

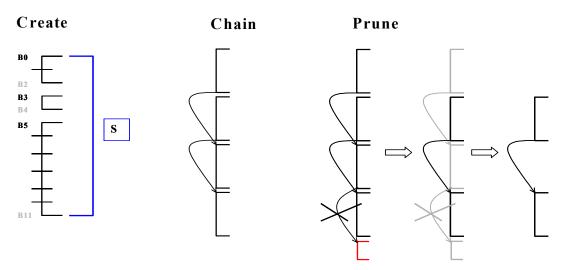

The segmentation algorithm divides the disassembly into chunks of segments containing *valid* instructions. It finds all the potential valid segments in the code and discards the invalid segments. However, overlapping segments can generate false positives. Segmentation deletes some segments that lead to invalid instructions; however, in order to delete the potential segments that lead to invalid segments, other methods are required. We use *chaining* to delete the segments that cannot logically be real. This allows regeneration of precise assembly. This chapter elaborates on the following points:

- Segment Chaining

- Segment Pruning

#### 5.1 Segment-Chaining

A segment can either terminate at an instruction that explicitly modifies the PC, or it can be an intermediate segment. In the former case, it is possible to chain the segments through direct *jumps* or *calls*. For example when a segment A ends with an explicit jump (direct jump) to segment B. It can be chained to the beginning of B. We then say, "Segment A points to segment B" or "Segment A leads to segment B" or "segment A points to byte b" (byte b does not start a segment).

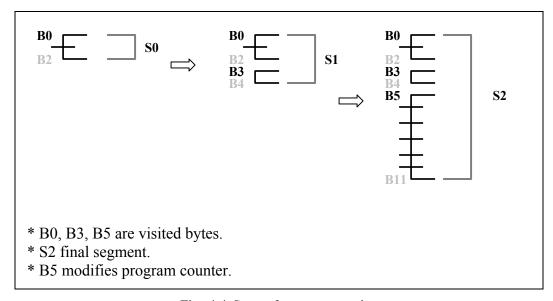

While chaining a segment *S*, if some segment in the path is pointing to a bad byte or data byte (i.e. byte does not start a segment) we discard *S*. We also discard all the segments pointing to *S*. Fig. 5-1 depicts various stages of segmentation. The chaining stage shows segment chaining by direct jumps. While the pruning stage shows the result

of pruning in case the jump target of some segment is a corrupt byte or byte that does not start any segment.

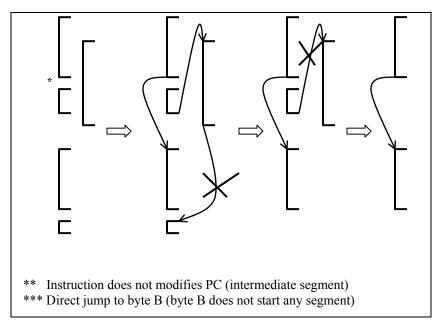

Fig. 5-1. Various stages of segmentation

Since we make an intermediate segment point to its master, the intermediate segment points to the same target locations where its master is pointing. If the master segment is pruned in the chaining process, we delete all the intermediate segments of this master segment. In a close to linear traversal of the segments, we can identify and discard most potential segments that lead to the non-instruction byte. Fig. 5-2 and Fig. 5-3 show the algorithm to connect all the segments as "one chunk" and it prunes all the segments that lead to a non-instruction.

## 5.2 Algorithm: Chaining and Pruning

Chaining finds all the segments and connects them through edges determined by direct jump targets. In case the target location of a segment S is corrupt or an invalid byte S gets pruned, then all the segments pointing to S also gets pruned. The segment can end by any one of the four types of instruction:

• Conditional direct jump,

- Unconditional direct jump,

- Indirect jump (not handled by chaining algorithm) or

- Any arbitrary instruction (Segment is an intermediate segment)

The following steps trace through the waypoints shown in the Fig. 5-2.

- 1. The positive PSS value v for any byte b denotes start of a segment of length v.

- 2. If the last instruction of a segment S is either the conditional or unconditional direct jump, the target location is verified for starting a valid segment S'. In case S' is a valid segment S is chained to starting location of S'. Otherwise S is discarded.

- 3. In case the last instruction of a segment S is a conditional jump, the next byte (*jbNext*) to the branching instruction is also verified along with jump target (*jb*) for potentially starting a segment S". If it starts a segment then S and S" are chained. If both *jb* and *jbNext* do not start valid segments, then S is discarded.

- 4. If the last instruction of a segment S is any arbitrary instruction that does not explicitly modify PC, it implies that S is an intermediate segment of a master segment M. In such a case, we chain S with starting location of M.

```

for (i = 0; i < length(program); i++)

jbNext=-1:

if (getPSS(b)>0)

1.

if (last instruction of Segment(b) is a direct jump )

jb = address of the target of the jump;

if (conditional jump)

{ jbNext = next byte after segment(b); }

if (validAddress(jb))

2.

if (getPSS(jb) == 0 \&\& jbNext == -1)

deleteSegment(b);

else if ( getPSS(jb) > 0 )

create an edge from b to jb

else if (getPSS(jb) < 0)

create an edge form b to jb + getPSS(jb)

3.

if (validAddress(jbNext)

if (getPSS(jb) == 0 \&\& getPSS(jbNext) == 0)

deleteSegment(b);

else if (getPSS(jbNext) > 0)

create an edge from b to jbNext

else if (getPSS(jbNext) < 0)

create an edge form b to jbNext + getPSS(jbNext)

if (! (validAddress(jb) && validAddress (jbNext)))

deleteSegment(b);

4.

} else if ( last instruction of Segment(b) does not modify PC ) {

create an edge from b to masterSegment(jb);

```

Fig. 5-2. Pseudocode for segment-chaining algorithm, Leftmost column specifies code waypoints.

```

deleteSegment(b)

{

for each segment i having edge to segment b

{    deleteSegment(i);  }

Segment(b)=null;

}

```

Fig. 5-3. Pseudocode for deleting a segment

## 5.3 Example: Segment Chaining and Pruning

Fig. 5-4 shows some cases of segments and how the chaining and pruning is done to these segments to reduce the false positives. The figure is showing chaining and ripple effect in deleting the invalid segments when a segment hits a bad byte.

Fig. 5-4. Example showing segment pruning by chaining

Fig. 5-4 depicts a segment in its various stages of chaining. A deletion of an edge leads to deletion of the segment. Deletion is marked by symbol *X* on the edges.

#### **6** Evaluation and Results

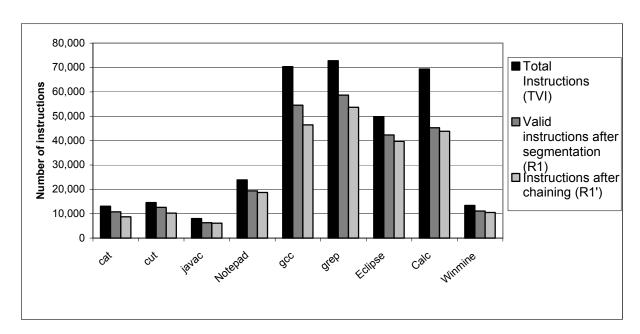

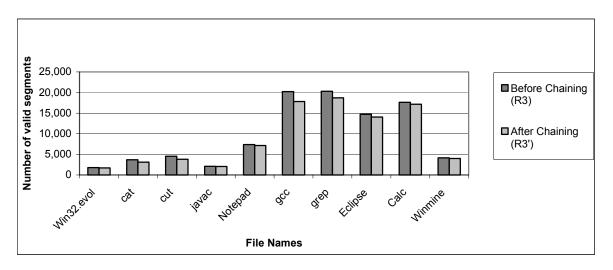

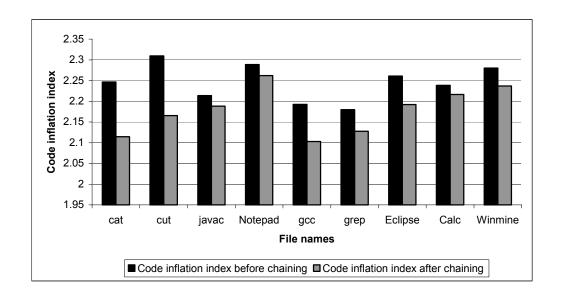

This section presents the performance evaluation of the proposed algorithms and highlights the limitations faced by them. The experimental setup for the evaluation is also presented. The main aim of this experiment is to study the percentage of valid instructions and the percentage of reducible false positives in a given binary, after applying the proposed algorithm. We divide the binaries into three different classes: first is class of clean Windows™ executables (e.g. notepad.exe), second is a class of malicious executables, and finally a class of non-executable† files. The evaluation measures of interest are: number of valid instructions in a binary (baseline), amount of false positives with respect to baseline, effect of chaining/pruning on these measures, and amount of code inflation.

#### 6.1 Theoretical Limitations and Assumptions

In the game of obfuscation/deobfuscation, the fewer assumptions the disassembler makes, the harder it is for hostile programmers to attack the static analysis. The main threat in the context of malice is missing malicious code. False positives might give an imprecise disassembly, but false negatives are the real threats, that give unsafe disassembly. Our proposed solution does not give any false negatives, if the binary satisfies certain assumptions.

#### **6.1.1** Attacking the Assumptions

This subsection discusses the limitations of our solution, and how malicious code writers can attack it. Let's look at the code snippet from worm Netsky.Z

\_

<sup>&</sup>lt;sup>†</sup> Non-executable files include image files as well as compressed files.

Self-modifying code: The example in Fig. 6-1 shows code that self modifies itself as it executes. Self-modifying code can cause disassemblers to miss some code because the instructions are generated at runtime, so what once was data could become code in the future and vice versa. Prior algorithms silently fail after giving few disassembled instructions as evident from Fig. 6-1, which shows disassembly results from an open source debugger Ollydbg. It stops disassembling after location 00403E6F. Disassembling starting at each byte may miss only the instruction starting at 00403E6E. However, self-modifying code can increase false negative manifolds if the code shown is repeated or tweaked slightly and then repeated. The segmentation algorithm cannot handle this attack.

| Location     |               | Column 1                       | Column 2                                        |  |  |  |  |  |

|--------------|---------------|--------------------------------|-------------------------------------------------|--|--|--|--|--|

|              | Hex           | Disassembly                    | Hex Disassembly                                 |  |  |  |  |  |

| 00403E5F     | B8 6E3E4000   | MOV EAX, 00403E6E              | B8 6E3E4000 MOV EAX, 00403E6E                   |  |  |  |  |  |

| <br>00403E64 | 8000 28       | ADD BYTE PTR DS:[EAX],28       | 8000 28 ADD BYTE PTR DS:[EAX],28                |  |  |  |  |  |

| <br>00403E67 | 40            | INC EAX                        | 40 INC EAX                                      |  |  |  |  |  |

| 00403E68     | 8100 67452301 | ADD DWORD PTR DS:[EAX],1234567 | 8100 67452301 ADD DWORD PTR<br>DS:[EAX],1234567 |  |  |  |  |  |

| <br>00403E6E | 90            | NOP                            | B8 32BC5C00 MOV EAX, 005CBC32                   |  |  |  |  |  |

| 00403E6F     | CB            | RETF                           | ,                                               |  |  |  |  |  |

| 00403E70     | 76            | DB 76                          |                                                 |  |  |  |  |  |

| 00403E71     | 39            | DB 39                          |                                                 |  |  |  |  |  |

| 00403E72     | FF            | DB FF                          |                                                 |  |  |  |  |  |

| 00403E73     | 50            | DB 50                          | 50 PUSH EAX                                     |  |  |  |  |  |

Fig. 6-1. Runtime self-modifying obfuscation (Netsky.Z)